ASIC

DESIGN

Cosa significa progettare circuiti integrati su misura

La progettazione ASIC (Application-Specific Integrated Circuit) rappresenta una scelta strategica per aziende che richiedono soluzioni ad alte prestazioni, affidabili e personalizzate. Microtest si propone come partner tecnologico per la realizzazione di circuiti integrati su misura, offrendo un approccio completo e flessibile, dal concept alla validazione finale. Grazie a competenze verticali e a una lunga esperienza nel settore, garantiamo risultati di alta qualità, ottimizzati per le esigenze specifiche di ogni applicazione.

La progettazione di un ASIC consiste nello sviluppo di circuiti integrati finalizzati a svolgere una funzione specifica all’interno di un sistema elettronico. Rispetto ai componenti generici (COTS) e ai progetti basati su componenti proprietari (COT), un ASIC garantisce prestazioni elevate, consumi ridotti e un fattore di forma compatto.

Gli ASIC sfruttano tecnologie VLSI (Very Large Scale Integration) per ottenere un’elevata densità di transistor e garantire la piena integrazione tra circuiti analogici e digitali. Questo si traduce in dispositivi affidabili, efficienti e ottimizzati sui parametri critici.

Caratteristiche

La progettazione ASIC è una disciplina strategica nell’industria microelettronica: consente di ottenere circuiti integrati su misura per requisiti di performance, affidabilità e miniaturizzazione, garantendo un’elevata efficienza e un’ottimizzazione dei costi su tutto il ciclo di vita del prodotto.

Design analogico vs digitale: due mondi da integrare

Nella progettazione di circuiti integrati su misura, la sinergia tra design analogico e design digitale è la chiave per ottenere ASIC ad alte prestazioni, capaci di rispondere a esigenze di precisione, velocità e affidabilità.

Il design analogico gestisce segnali continui sia nel tempo che nell’ampiezza, tipicamente derivanti dalla conversione di grandezze fisiche reali, come temperatura, pressione, luce, in segnali elettrici utilizzabili, oppure destinati a pilotare specifici trasduttori. La progettazione di circuiti analogici richiede un’attenta considerazione di molteplici fattori che possono influenzare le prestazioni finali, tra cui la variabilità del processo tecnologico, la temperatura operativa, gli effetti piezoelettrici, gli accoppiamenti e i componenti parassiti introdotti dalla tecnologia di realizzazione. Si tratta di un’attività che opera a livello dei singoli componenti elementari – transistori, resistenze, capacità – i quali devono essere dimensionati in modo accurato per garantire il corretto funzionamento del circuito.

Il design digitale si concentra sulla gestione di segnali discreti, sia nel tempo che nell’ampiezza. Questa caratteristica consente di ottenere un’elevata robustezza al rumore e di incrementare significativamente la capacità di elaborazione dei segnali a parità di area, permettendo l’implementazione di funzioni anche molto complesse in spazi estremamente ridotti. La progettazione avviene a livello descrittivo, definendo funzionalità e comportamenti tramite linguaggi come il VHDL. Le principali problematiche da affrontare riguardano il rispetto dei vincoli temporali (timing), considerando anche le condizioni peggiori del processo tecnologico. Poiché il design digitale si basa su segnali discreti, è necessario prevedere circuiti analogici di interfaccia – come gli ADC (Analog-to-Digital Converter) – in grado di convertire i segnali continui provenienti dal mondo esterno in segnali digitali quantizzati. Analogamente, per pilotare trasduttori o attuatori, sono indispensabili convertitori DAC (Digital-to-Analog Converter), che trasformano i segnali digitali di uscita in segnali analogici.

La fusione di questi due ambiti consente di creare ASIC mixed-signal: soluzioni integrate in grado di combinare la sensibilità e la precisione analogica con la programmabilità e flessibilità del digitale. Questa integrazione è oggi imprescindibile in settori come medicale, automotive e industriale.

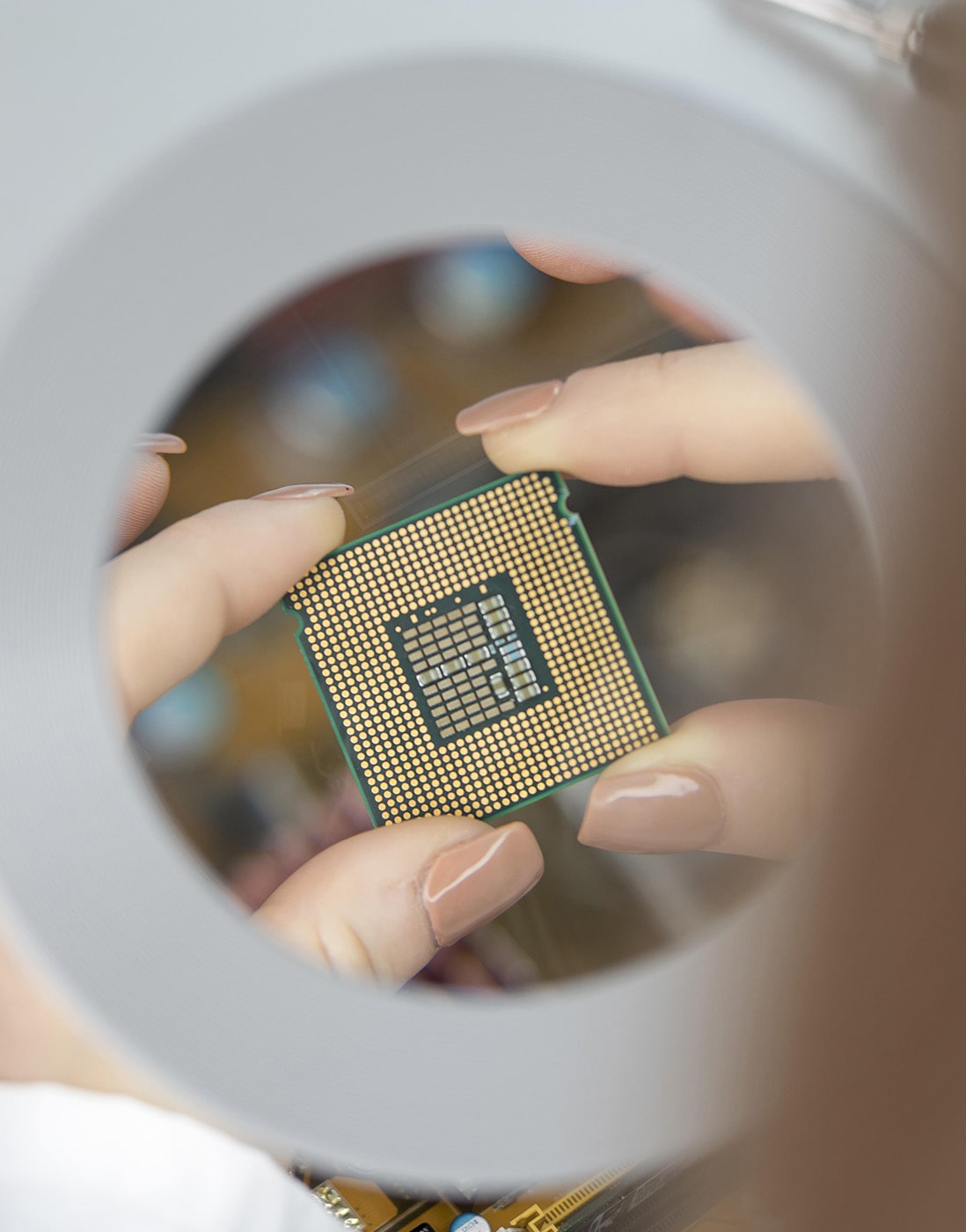

Cosa c'è dentro un ASIC: design e layout dei circuiti integrati

Le tecnologie: come è fatto un ASIC

Alla base della tecnologia CMOS vi è il transistor MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor), un dispositivo a effetto di campo con un gate isolato da un sottile strato di ossido. I MOSFET esistono in due configurazioni complementari: NMOS (canale N) e PMOS (canale P), utilizzati insieme per realizzare le logiche CMOS che ottimizzano consumi e prestazioni.

Nel mercato dell’elettronica consumer, la tecnologia predominante per la realizzazione degli ASIC è il CMOS (Complementary Metal-Oxide Semiconductor), basata proprio sull’uso dei transistor MOSFET. La forza del CMOS risiede nella sua capacità di integrare un numero crescente di transistor per unità di area, grazie a un processo chiamato scaling. Questo ha permesso lo sviluppo di livelli di integrazione VLSI (Very Large Scale Integration, fino a 10⁹ transistor/chip) e ULSI (Ultra Large Scale Integration, fino a 10¹⁰ transistor/chip). Tuttavia, i limiti fisici dello scaling stanno emergendo a causa degli effetti di canale corto, che incrementano la potenza statica dissipata. Per proseguire nella miniaturizzazione, si studiano nuove soluzioni tecnologiche, come materiali con costante dielettrica elevata (ossidi ad alto K), substrati a elevata mobilità e architetture innovative come la tecnologia SOI (Silicon On Insulator) e i dispositivi multi gate.

Un ASIC CMOS viene realizzato a partire da un substrato, in genere di tipo P (nella tecnologia CMOS a n-well). Inizialmente, aree drogate N (n-well) vengono formate per ospitare i transistor P-MOS. Si cresce poi uno strato di ossido di campo, che isola elettricamente le aree non attive. Sulle aree attive si crea un ossido più sottile (ossido di gate) su cui viene deposto il polisilicio, formando il gate del transistor. Le regioni non coperte da questo strato vengono drogate per creare le zone attive: N+ per i transistor NMOS (direttamente sul substrato) e P per i PMOS (all’interno dell’n-well).

Segue la deposizione di un isolante da fase vapore, rimosso selettivamente nelle aree di contatto, e la metallizzazione, che connette il gate e le aree attive. Strati successivi di ossido e metallizzazione possono essere aggiunti per realizzare interconnessioni multiple, terminando con uno strato di passivazione, rimosso solo in corrispondenza dei pad di contatto che collegano il chip ai pin del package tramite i fili di bonding.

Dall’idea al chip: le fasi del IC Design

La progettazione di un ASIC è un processo costituito da varie fasi, ciascuna delle quali è cruciale per il successo dell’ASIC stesso:

Il processo di progettazione di un ASIC inizia con l’analisi dettagliata della specifica, basata sul data sheet del dispositivo e sulle esigenze applicative. Il data sheet rappresenta il documento di riferimento che definisce i parametri elettrici e le funzionalità, costituendo la base per le successive decisioni progettuali.

Basandosi sulla specifica, il progettista definisce l’architettura complessiva dell’ASIC, suddividendolo in blocchi funzionali. Ogni blocco rappresenta un circuito che implementa una funzione mirata. La progettazione segue un approccio gerarchico, con diverse “viste” associate a ciascun blocco:

- Vista schematica: rappresenta il circuito tramite l’interconnessione di componenti elementari come MOSFET, resistori e condensatori.

- Vista simbolica: mostra solo i terminali del blocco, facilitando l’interconnessione con altri blocchi.

Questo approccio modulare semplifica la gestione della complessità del sistema e garantisce una progettazione più ordinata e scalabile.

La progettazione degli schematici inizia con la definizione delle funzionalità del blocco e dei segnali di interfaccia. Utilizzando un design editor integrato con il design kit fornito dalla fonderia, il progettista seleziona i componenti disponibili nella tecnologia scelta.

Il circuito viene quindi simulato per verificarne il comportamento e le prestazioni rispetto alla specifica. Le simulazioni considerano modelli accurati dei componenti, inclusi nel design kit, e permettono di ottimizzare il dimensionamento dei componenti.

Le simulazioni includono anche verifiche di:

- Design for Testability (DfT): inserimento di strutture ausiliarie per migliorare la testabilità, come multiplexer analogici di test mode e switch controllati per isolare i segnali durante il test.

- Design for Reliability: adozione di tecniche per garantire l’affidabilità nel tempo, come simulazioni di aging per valutare il drift dei parametri e implementazione di circuiti per limitare tali effetti.

- Design for Robustness: progettazione per garantire la robustezza contro fenomeni come ESD (Electrostatic Discharge) e EMC (Electromagnetic Compatibility).

Per garantire la qualità e l’affidabilità dell’ASIC, vengono implementate strategie di test specifiche:

- Testabilità interna: tensioni e correnti rilevanti vengono instradate verso il livello top dell’ASIC tramite multiplexer analogici, permettendo la misurazione durante il test senza influenzare le prestazioni operative.

- Stress test: applicazione di tensioni di stress su componenti critici, come power MOS, per identificare difetti latenti. Durante questi test, le circuiterie connesse vengono isolate tramite switch controllati.

- Test di leakage (IDDQ test): misura delle correnti di leakage per identificare difetti nei dispositivi CMOS. Per garantire l’efficacia del test, le correnti dei blocchi analogici vengono disabilitate e i nodi flottanti forzati a potenziali noti.

Queste strategie sono fondamentali per assicurare che l’ASIC funzioni correttamente nel tempo e in condizioni operative reali.

Fasi della progettazione ASIC: dal concept alla produzione

Il layout definisce fisicamente il chip, traducendo il progetto in maschere di processo che guidano la fabbricazione. Il floorplan stabilisce la disposizione ottimale dei macroblocchi, separando fisicamente e elettricamente blocchi rumorosi (es. oscillatori, regolatori switching) e blocchi sensibili (es. riferimenti di tensione, monitor). Ciò include duplicazioni di piste di alimentazione, uso di piani di massa dedicati e minimizzazione delle lunghezze delle piste, per limitare la resistenza parassita e migliorare l’affidabilità.

Tool avanzati eseguono verifiche di rispetto delle regole tecnologiche (Design Rule Checker – DRC) e la corrispondenza tra layout e schematico (Layout Versus Schematic – LVS).

Il layout introduce resistenze e capacità parassite che influenzano le prestazioni finali. Tool software dedicati estraggono questi parametri creando una “vista estratta” del circuito, che comprende accoppiamenti parassiti tra piste e verso massa. Le simulazioni post-layout utilizzano questa vista per verificare l’impatto dei parassiti e guidare eventuali modifiche: allargamento piste troppo resistive, spostamento di net rumorose, correzioni per migliorare l’integrità del segnale.

La progettazione digitale dell’ASIC si divide in due fasi principali:

- Front End:

- Progettazione funzionale e logica a livello RTL (linguaggi come VHDL o Verilog).

- Inserimento di strutture per la testabilità (Design for Test, scan chain, BIST).

- Simulazioni funzionali e di test per validare la logica prima della sintesi.

- Back End:

- Sintesi logica: conversione della logica RTL in netlist gate-level, con inserimento di Digital BIST e scan chain.

- Verifiche: copertura test, verifica formale di coerenza tra RTL e sintesi.

- Layout fisico: posizionamento, sintesi dell’albero di clock, routing, estrazione parassiti.

- Verifiche finali: analisi temporale (timing check), verifica energetica (power check), DRC e LVS per rispettare regole di progettazione.

- Post-layout: simulazioni finali, verifica della copertura dei test e rilascio dei pattern di test per ATE.

Simulazioni che integrano blocchi analogici e digitali, eseguite su tutto l’ASIC alimentato e stimolato tramite i pin esterni. Verificano la coerenza del sistema, la corretta comunicazione tra blocchi e la stabilità operativa in scenari reali, inclusi quelli di fault.

La produzione inizia con il file .gds contenente tutte le informazioni del layout. I wafer di silicio sono processati per realizzare i circuiti, quindi tagliati per ottenere i singoli die. Ogni die viene montato su un frame metallico e collegato tramite fili di bonding ai pin del package, che viene poi sigillato con resine plastiche o ceramiche per formare l’ASIC completo.

L’ASIC completato passa alla fase di validazione, durante la quale il progettista esegue test funzionali su schede appositamente realizzate per verificare la conformità alle specifiche. Parallelamente, il test engineer effettua la caratterizzazione utilizzando ATE, misurando i parametri elettrici e calcolando l’indice Cpk, che fornisce indicazioni sulla capacità produttiva e la stabilità del processo industriale.

Se la validazione o la caratterizzazione evidenziano discrepanze rispetto alle specifiche o un valore di Cpk troppo basso, si procede con un redesign. Questa fase permette di ottimizzare i circuiti e assicurare la piena rispondenza ai requisiti, garantendo la robustezza e la resa produttiva.

La qualifica finale dell’ASIC prevede test rigorosi (es. AEC-Q100) che simulano condizioni La qualifica finale dell’ASIC prevede test severi, come quelli definiti dallo standard AEC-Q100 per il settore automotive. Il dispositivo viene sottoposto a cicli di temperatura, pressione e umidità per verificare la tenuta dei parametri critici. Queste prove simulano condizioni operative estreme e confermano la robustezza e la stabilità dell’ASIC e del suo package, certificandone l’idoneità all’applicazione.

Storie di successo nella progettazione di ASIC personalizzati

Scopri come i circuiti integrati personalizzati hanno trasformato le prestazioni, l’efficienza e l’affidabilità in tutti i settori, dall’ideazione al silicio, grazie all’esperienza ASIC end-to-end di Microtest.

Contattaci

Glossario

-

ASIC (Application-Specific Integrated Circuit)

Circuito integrato progettato e realizzato per svolgere una funzione specifica e ottimizzata in un’applicazione elettronica. A differenza dei circuiti standard, offre elevate prestazioni, efficienza energetica e personalizzazione completa.

-

MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)

Transistor a effetto di campo con gate isolato da un sottile strato di ossido. È il componente base della tecnologia CMOS, grazie alla sua capacità di commutazione rapida e al basso consumo statico.

-

CMOS (Complementary Metal-Oxide Semiconductor)

Tecnologia che combina transistor NMOS e PMOS per ridurre il consumo statico e aumentare l’efficienza delle logiche digitali e analogiche integrate.

-

VLSI (Very Large Scale Integration)

Tecnologia di integrazione che permette la realizzazione di circuiti con centinaia di milioni di transistor su un singolo chip, garantendo compattezza e performance elevate.

-

ULSI (Ultra Large Scale Integration)

Evoluzione del VLSI che consente di superare la soglia del miliardo di transistor per chip, spingendo la miniaturizzazione e la complessità circuitale a livelli estremi.

-

Layout

Rappresentazione fisica dettagliata del circuito integrato, comprendente maschere di processo, metallizzazioni, aree di contatto e isolamenti. È il passaggio finale prima della produzione in fonderia.

-

Floorplan

Fase di piazzamento dei blocchi funzionali all’interno dell’ASIC, con attenzione alla separazione fisica ed elettrica tra aree sensibili e rumorose, alla minimizzazione delle lunghezze delle piste e all’ottimizzazione delle alimentazioni.

-

ESD (Electrostatic Discharge)

Fenomeno di scarica elettrostatica che può danneggiare i componenti elettronici. La protezione ESD è fondamentale per la robustezza e l’affidabilità a lungo termine del dispositivo.

-

EMC (Electromagnetic Compatibility)

Capacità di un circuito di operare senza interferire né essere disturbato da altri sistemi elettronici. Implica sia la riduzione delle emissioni elettromagnetiche sia la capacità di resistere a disturbi esterni.

-

Drift / Aging

Graduale variazione dei parametri elettrici di un dispositivo durante la vita utile, dovuta a fenomeni di invecchiamento dei materiali e stress operativi.

-

Design for Testability (DfT)

Approccio di progettazione che prevede l’inserimento di circuiterie e interfacce dedicate a facilitare il collaudo, migliorare la copertura di test e ridurre i costi di verifica.

-

ATE (Automatic Test Equipment)

Apparati automatici avanzati per il testing di dispositivi elettronici, utilizzati in fase di caratterizzazione e produzione per misurare le prestazioni e verificare la conformità alle specifiche.

-

Cpk (Process Capability Index)

Indice statistico che misura la capacità del processo produttivo di mantenere i parametri dei dispositivi entro i limiti di specifica, rappresentando un indicatore diretto della qualità industriale.

-

FIT (Failure In Time)

Parametro che esprime la probabilità di guasto di un componente in un miliardo di ore di funzionamento, usato per quantificare l’affidabilità nel tempo.

-

SIL (Automotive Safety Integrity Level)

Classificazione che indica il livello di sicurezza richiesto per un dispositivo elettronico in applicazioni automotive, con quattro livelli (A–D) crescenti in termini di criticità e requisiti di sicurezza.

-

DFMEA (Design Failure Mode and Effects Analysis)

Analisi qualitativa dei guasti sistematici e dei loro effetti sul funzionamento dell’ASIC, basata su parametri come severità, detection e occorrenza.

-

DFMEDA (Design Failure Mode, Effects and Diagnostic Analysis)

Analisi quantitativa dei guasti randomici e della copertura diagnostica (diagnostic coverage) dei monitor e dei meccanismi di protezione integrati.